MEMS器件的制作方法以及MEMS器件与流程

本申请涉及半导体,具体而言,涉及一种mems器件的制作方法以及mems器件。

背景技术:

1、作为滤波器芯片的mems(micro electro mechanical system,微机电系统)器件,需要在最后一步把牺牲层材料去除,该过程称为释放工艺。为了阻挡不需要被腐蚀的区域,会设置阻挡层。现有技术中,去除牺牲层材料的过程中,会由于原电池效应使阻挡层被腐蚀,从而造成不需要被腐蚀的区域也会被部分或者全部去除,影响器件性能甚至造成器件失效。

技术实现思路

1、本申请的主要目的在于提供一种mems器件的制作方法以及mems器件,以解决现有技术的mems器件制作过程中去除牺牲层时,阻挡层易被腐蚀,从而影响器件性能的问题。

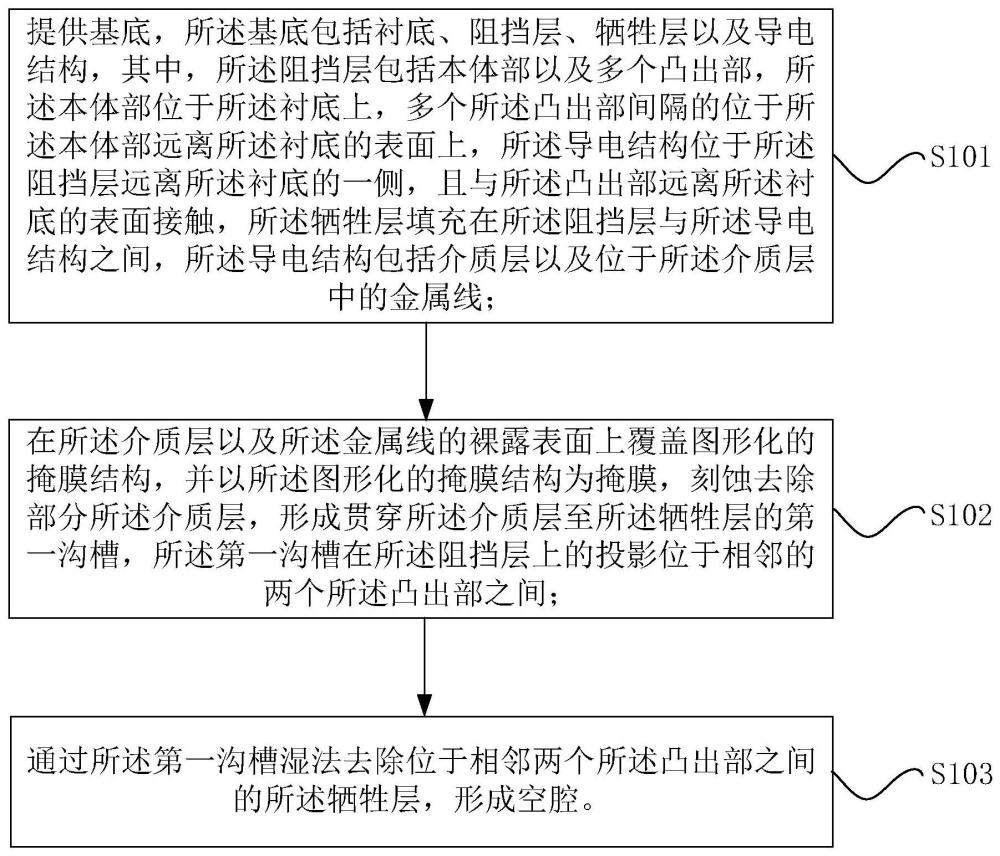

2、为了实现上述目的,根据本申请的一个方面,提供了一种mems器件的制作方法,包括:提供基底,所述基底包括衬底、阻挡层、牺牲层以及导电结构,其中,所述阻挡层包括本体部以及多个凸出部,所述本体部位于所述衬底上,多个所述凸出部间隔的位于所述本体部远离所述衬底的表面上,所述导电结构位于所述阻挡层远离所述衬底的一侧,且与所述凸出部远离所述衬底的表面接触,所述牺牲层填充在所述阻挡层与所述导电结构之间,所述导电结构包括介质层以及位于所述介质层中的金属线;在所述介质层以及所述金属线的裸露表面上覆盖图形化的掩膜结构,并以所述图形化的掩膜结构为掩膜,刻蚀去除部分所述介质层,形成贯穿所述介质层至所述牺牲层的第一沟槽,所述第一沟槽在所述阻挡层上的投影位于相邻的两个所述凸出部之间;通过所述第一沟槽湿法去除位于相邻两个所述凸出部之间的所述牺牲层,形成空腔。

3、可选地,提供基底,包括:提供所述衬底、所述阻挡层以及牺牲层;在预定表面上依次叠置第一介质子层以及第一导电子层,并在所述第一导电子层的裸露表面上以及所述牺牲层的裸露表面上依次叠置第二初始介质子层、第二初始导电子层和第三初始介质子层,所述预定表面包括所述阻挡层远离所述衬底的部分表面;依次去除部分的所述第三初始介质子层、部分的所述第二初始导电子层以及部分的所述第二初始介质子层,使得部分的所述第一导电子层裸露,形成第二沟槽,剩余的所述第二初始介质子层形成第二介质子层,剩余的所述第三初始介质子层形成第三介质子层,剩余的所述第二初始导电子层形成第二导电子层,所述第三介质子层、所述第二导电子层、所述第二介质子层、所述第一导电子层以及所述第一介质子层构成所述介质层;在所述第二沟槽的底部和侧面形成所述金属线,得到所述基底。

4、可选地,提供所述衬底、所述阻挡层以及牺牲层,包括:提供所述衬底;在所述衬底上形成第四介质子层,所述第四介质子层包括第一本体子部以及多个凸出子部,多个所述凸出子部间隔地位于所述第一本体子部上;在所述第四介质子层远离所述衬底的表面上形成阻挡子层,所述阻挡子层包括第二本体子部以及多个包裹部,所述第二本体子部覆盖在所述第一本体子部上,所述包裹部覆盖所述凸出子部的裸露表面,所述第一本体子部以及所述第二本体子部构成所述本体部,所述凸出子部以及所述包裹部构成所述凸出部,所述第四介质子层以及所述阻挡子层构成所述阻挡层;在所述本体部远离所述衬底的表面上以及所述凸出部的侧壁上形成所述牺牲层,所述牺牲层远离所述衬底的表面与所述凸出部远离所述衬底的表面平齐。

5、可选地,相邻的两个所述凸出部分别为第一凸出部和第二凸出部,所述第一凸出部远离衬底的表面与所述衬底的距离为第一距离,所述第二凸出部远离衬底的表面与所述衬底的距离为第二距离,所述第一距离大于所述第二距离。

6、可选地,在预定表面上依次叠置第一介质子层以及第一导电子层,并在所述第一导电子层的裸露表面上以及所述牺牲层的裸露表面上依次叠置第二初始介质子层、第二初始导电子层和第三初始介质子层,包括:在所述第二凸出部远离所述衬底的表面上以及位于所述第二凸出部两侧的所述牺牲层远离所述衬底的表面上形成所述第一介质子层;在所述第一凸出部和所述第二凸出部之间的所述牺牲层远离所述衬底的表面上以及所述第一介质子层远离所述衬底的表面上形成所述第一导电子层;在所述第一导电子层远离所述衬底的表面上、所述第一凸出部远离所述衬底的表面上以及所述第一凸出部两侧的所述牺牲层远离所述衬底的表面上依次叠置所述第二初始介质子层、所述第二初始导电子层和所述第三初始介质子层。

7、可选地,通过所述第一沟槽湿法去除部分的所述牺牲层,使得位于相邻两个所述凸出部之间的所述牺牲层裸露,形成空腔,包括:沿所述第一沟槽注入缓冲氧化物腐蚀液,以腐蚀去除部分的所述牺牲层,形成所述空腔。

8、可选地,所述缓冲氧化物腐蚀液与所述牺牲层的反应速率大于所述缓冲氧化物腐蚀液与所述阻挡层的反应速率。

9、可选地,所述阻挡层的材料包括多晶硅,所述牺牲层的材料包括磷硅玻璃。

10、可选地,所述图形化的掩膜结构的材料包括光刻胶或pi(polyimide,聚酰亚胺)胶。

11、根据本申请的另一方面,提供了一种mems器件,所述mems器件为采用任一种所述的方法制作得到的。

12、应用本申请的技术方案,在本申请的mems器件的制作方法中,首先,提供包括衬底、阻挡层、牺牲层以及导电结构的基底,其中,导电结构包括介质层和位于介质层中的金属线,阻挡层包括位于衬底上的本体部和间隔设置在本体部上的多个凸出部,导电结构位于阻挡层远离衬底的一侧,且仅和凸出部的顶部接触,这样通过凸出部在导电结构和本体部之间隔出了多个空隙,牺牲层填充在多个空隙中;然后,在介质层以及金属线的裸露表面上覆盖图形化的掩膜结构,并以图形化的掩膜结构为掩膜,刻蚀去除部分介质层,形成在所述阻挡层上的投影位于相邻的两个所述凸出部之间,贯穿介质层至牺牲层的第一沟槽;最后,通过第一沟槽湿法去除部分的牺牲层,形成空腔。相比于现有技术的mems器件制作过程中去除牺牲层时,阻挡层易被腐蚀,从而影响器件性能的问题,本申请在对基底进行湿法刻蚀之前,形成了覆盖金属线裸露表面的掩膜结构,这样在湿法刻蚀过程中湿法腐蚀液不会与金属材料接触,从而避免了由于湿法腐蚀液中的离子影响,产生阻挡层-介质层-金属线的电流回路,有效消除了原电池效应,保证了阻挡层不会在去除牺牲层的过程中由于原电池效应被腐蚀,从而保证了得到的空腔形态较好、器件性能较好。

技术特征:

1.一种mems器件的制作方法,其特征在于,包括:

2.根据权利要求1所述的方法,其特征在于,提供基底,包括:

3.根据权利要求2所述的方法,其特征在于,提供所述衬底、所述阻挡层以及牺牲层,包括:

4.根据权利要求2所述的方法,其特征在于,相邻的两个所述凸出部分别为第一凸出部和第二凸出部,所述第一凸出部远离衬底的表面与所述衬底的距离为第一距离,所述第二凸出部远离衬底的表面与所述衬底的距离为第二距离,所述第一距离大于所述第二距离。

5.根据权利要求4所述的方法,其特征在于,在预定表面上依次叠置第一介质子层以及第一导电子层,并在所述第一导电子层的裸露表面上以及所述牺牲层的裸露表面上依次叠置第二初始介质子层、第二初始导电子层和第三初始介质子层,包括:

6.根据权利要求1至5中任一项所述的方法,其特征在于,通过所述第一沟槽湿法去除位于相邻两个所述凸出部之间的所述牺牲层,形成空腔,包括:

7.根据权利要求6所述的方法,其特征在于,所述缓冲氧化物腐蚀液与所述牺牲层的反应速率大于所述缓冲氧化物腐蚀液与所述阻挡层的反应速率。

8.根据权利要求1至6中任一项所述的方法,其特征在于,所述阻挡层的材料包括多晶硅,所述牺牲层的材料包括磷硅玻璃。

9.根据权利要求1至6中任一项所述的方法,其特征在于,所述图形化的掩膜结构的材料包括光刻胶或pi胶。

10.一种mems器件,其特征在于,所述mems器件为采用权利要求1至9中任一项所述的方法制作得到的。

技术总结

本申请提供了一种MEMS器件的制作方法以及MEMS器件,该方法包括:提供基底,基底包括衬底、阻挡层、牺牲层以及导电结构,其中,阻挡层包括本体部以及多个凸出部,本体部位于衬底上,多个凸出部间隔的位于本体部远离衬底的表面上,导电结构位于阻挡层远离衬底的一侧,且与凸出部远离衬底的表面接触,牺牲层填充在阻挡层与导电结构之间,以图形化的掩膜结构为掩膜,刻蚀去除部分介质层,形成贯穿介质层至牺牲层的第一沟槽,沟槽在阻挡层上的投影位于相邻的两个凸出部之间;通过第一沟槽湿法去除位于相邻两个凸出部之间的牺牲层形成空腔。本申请解决了现有技术中MEMS器件制作过程中影响器件性能的问题。

技术研发人员:万星星,王晋,郝伟倩,俞开园,高晋文,郭佳惠

受保护的技术使用者:润芯感知科技(南昌)有限公司

技术研发日:

技术公布日:2024/8/21

技术研发人员:万星星,王晋,郝伟倩,俞开园,高晋文,郭佳惠

技术所有人:润芯感知科技(南昌)有限公司

备 注:该技术已申请专利,仅供学习研究,如用于商业用途,请联系技术所有人。

声 明 :此信息收集于网络,如果你是此专利的发明人不想本网站收录此信息请联系我们,我们会在第一时间删除